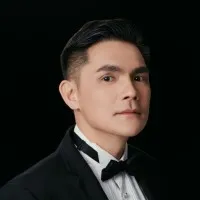

Keng Kooi Lim

Backend Assembly and Testing Principle Engineer

Connect with Keng Kooi Lim to Send Message

Connect

Connect with Keng Kooi Lim to Send Message

ConnectTimeline

About me

New Product and HVM Product Manager at Intel | Testing | YIELD, REL Improvement | New Product Qualification | Pre and Post Si Validations | Tape Development | NPI Program Lead | Wafer fab and Assembly Manufacturing

Education

National University of Singapore

-Master of Science - MS Major in the Semiconductor

Nanyang Technological University

-Bachelor Degree of EEE Electrical and Electronics Engineering

Experience

Micron Technology

Aug 2002 - Feb 2010Backend Assembly and Testing Principle EngineerProduct Lead, working on the memory DRAM and Nand MomoryKey responsible included:- Backend yield improvement, electrical failure analysis, communication with FAB to improve backend yield.

IM Flash

Mar 2011 - Jan 2015Fab Manufacturing Principle Product and REL Engineer LeadWorking on 2D Nand, 3D Nand and the 3D XPoint Memory Products.Product lead, responsible included Product Yield Improvement, Solving REL issue, New Product Qualification, process deviation disposition, training.Awarded Best Product and REL Technical Lead in the company

Intel Corporation

Dec 2015 - Jun 2017Fab Product ManagerStartup new 3D Nand Wafer Fab Manufacturing in Intel Dalian, China. Setup new Fab Product team in the 3D Nand Fab.Solve 3D Nand Product, Yield and REL issue and qualify 3D nand product.

Intel Corporation

Aug 2018 - nowDirector New Product Development• Leading Product and TEst organization with groups 40 engineers globally (from USA, China Dalian, Shanghai), with 3 senior managers direct report. • Set up Fab Product Technology Development organization from the green field. Experienced in recruiting and growing world-class teams.• Key responsibilities of the organization are the Sort tape development, Pre and Post Si debug, design validation, Pre-Si simulation, Sort Test Time Reduction, Yield/REL improvement/debugging and product qualification and ramping activities.• Successfully ramping 3 technology nodes, 5 products, 7 test chips in the past 5 years with a good track record help team members, supervisors, companies, and customers success.• Selected as Intel Excellent Manager Award in 2022. Show less

Licenses & Certifications

- View certificate

Certified ScrumMaster® (CSM®)

Scrum AllianceSept 2021

Languages

- enEnglish

- chChinese

- thThai

- maMalay

Recommendations

Steven summers

Installation Technician at Simplex GrinnellReading, Pennsylvania, United States

Marvin erdner

Irgendwas mit Schreiben. | OMR Reviews | Sponsored, SEO, internHamburg, Hamburg, Germany

Magemybindo c

"""Competent HR Assistant | Building and Improving Workplace Relations with MS Office & HRMIS Skills"""Tamil Nadu, India

Tanya turner

Director at Turnto Consultants (Pty) LtdCity of Johannesburg, Gauteng, South Africa

Shiyambarath s

Assistant Manager (DataCenter & Infrastructure Operations), Vulnerability and Patch AdministratorBengaluru, Karnataka, India

Vidhu tripathi

Cluster Operation Manager - (HL and LAP)at SMFGLucknow, Uttar Pradesh, India

Kezia gigy

Food EngineerKottayam, Kerala, India

Malwina maroszek

Malwina MaroszekGrójec, Mazowieckie, Poland

Sean scroggie

Clinical Trial Associate II at BDD PharmaGlasgow, Scotland, United Kingdom

Yousef saleh

IT Specialist @ City of Dearborn | Cybersecurity @EMU |Security+Dearborn, Michigan, United States

George stasinos

Product Manager| Product Owner | Product Development | Solution Design | Focus on Business Value | A...Limassol, Cyprus

John michael anthony lucas

Store LeaderLorton, Virginia, United States

Ekta choudhary

Technical Recruiter/Program Coordinator @ TekWissen ® | Learning LinkedIn RecruiterBengaluru, Karnataka, India

Kalpan shah

Tech Entrepreneur | Helping Founders with SaaS ProductsAhmedabad, Gujarat, India

Siddhant kulharia

Software Engineer 1 at Precisely | Fullstack Developer | AWS | Angular | Microservices | Distribute...Chandigarh, Chandigarh, India

David hidalgo ramos

Senior Technical Solutions at CriteoBarcelona, Catalonia, Spain

Nagendra d, cua™

Product, UX, Interaction DesignerBengaluru, Karnataka, India

Rishav .

| Lean Six Sigma, Project Management | Quality Control | OSP EngineerBilaspur, Himachal Pradesh, India

Ashley roosa

Director of Parent Relations and Special Events at Collegiate SchoolNew York City Metropolitan Area

邓振辉

海康—机器视觉Guangzhou, Guangdong, China

...

Deep Enrich

Deep Enrich