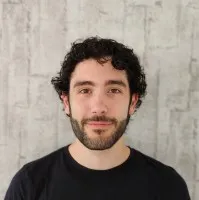

李浩

ASIC Engineer

Connect with 李浩 to Send Message

Connect

Connect with 李浩 to Send Message

ConnectTimeline

About me

Staff Engineer ASIC at Seagate Technology

Education

Shanghai institute of microsystem and information technology

1998 - 2001Master’s Degree MEMS

武汉大学

1994 - 1998Bachelor’s Degree 半导体物理学

Experience

华为

Apr 2001 - Oct 2006ASIC EngineerBaseband processor chip of WCDMA mobile phone Setup verification environment of baseband processor of WCDMA for mobile phone Be responsible for verification environment and verification of Cell search, multi-wave search and multi-wave merge block Using Verilog, SystemC. Knowledge about WCDMA baseband and HFWave shaping of multi-carrier research of WCDMA Design FPGA and verify it for wave shaping of multi-carrier of WCDMA Performance testing of wave shaping in validation platform Show less

LSI, an Avago Technologies Company

Oct 2006 - Aug 2014Staff ASIC EngineerACP5500(Advanced Network Co-Processor) verificationLCP(Link layer Network Co-Processor) verification and emulation Be responsible for SAS(Slow-Access-Subblock) block verification. Setup the SAS block verification environment and do testing for SAS and the sub-blocks of SAS, such as UART, I2C, MDIO, USB, SPI, TRNG, Timer, GPIO, etc. Knowledge about SystemVerilog, OVM, ARM, BusMatrix AXI/AHB/APB, Dickens, etc.UltraMapper(SDH/SONET) Validation and emulation Test UltraMapper chip on board. Setup validation platform and test whole chip testcases on board.UltraMapper verification Setup UltraMapper verification environment and do test.Responsible for verification of ATCA, STS3C, TPGC, SPEMPR, STS1LT, etc.Using SpecmanE. Knowledge about SDH/SONET Show less

Seagate Technology

Sept 2014 - nowStaff Engineer ASICGriffin/Neptune/Mars(Product name of Solid Static Disk Controller) emulation Using FPGA board, chip board or Palladium to verify ASIC design Focus on Core block emulation, including MAP, packer/unpacker, MPU, CMS, DMA,etc. Using C/C++, GDB, Shell, Python, Tensilica architecture(CPU), Palladium

Licenses & Certifications

Master of Microelectronics and Solid State Electronics

Shanghai Institute of Metallurgy, Chinese Academy of Sciences

Languages

- chChinese

- enEnglish

Recommendations

Giang nguyen

Digital Executive | GroupM VietnamHo Chi Minh City, Vietnam

Ana fallas

Manager EMEIA Tax Centre - Operating Model Effectiveness at EYAmsterdam, North Holland, Netherlands

Anil kumar

professor at UPESDelhi, India

Martin takov

Sales Manager @ MINI EastrandCity of Johannesburg, Gauteng, South Africa

Tom pelleymounter

Electrical Engineer self employedUnited Kingdom

Virendra choudhary

--Spraynt Technologies - Web Design | Mobile App Development | Digital Marketing Company

Simphiwe simelane

Project Coordinator at eSTUDY South Africa| HUMANITARIAN|HONS. PSYCHOLOGY|BA BEHAVIOURAL SCIENCES|HU...Pretoria, Gauteng, South Africa

Shalvi gupta

Molecular and Cell Biology student at the University of ConnecticutNashua, New Hampshire, United States

Pablo smolkin

FPGA Verification Engineer @ Skyloom Global | Assistant Professor @ ITBAArgentina

Garron nieuwenhuis

Experienced Payments Industry Leader | Sales Strategist | Product and Project ManagerJeffreys Bay, Eastern Cape, South Africa

Cauê takeuchi romano

Team Manager | Customer Support Specialist | Customer Care Analyst | Frontend DeveloperEchizen, Fukui, Japan

Sidharth raj khandelwal

Aspiring Full Stack Developer | Graduate Student at Pace University | Ex-TietoEVRY Software Engineer...Jersey City, New Jersey, United States

Ben white

Technology Degree Apprentice at PwC UKLeeds, England, United Kingdom

Shakil hosen

SQL, Python, ML, Data analysis and Data VisualizationDhaka, Bangladesh

Supreetha bv

Recruiting Analyst | AccentureBengaluru, Karnataka, India

Marcela alvarez

Inovação | Gestão de Comunidades | Gestão de Projetos | Startups | EventosSão Paulo, São Paulo, Brasil

Al-hussein a.satar

IT Engineer || Systems Administrator || Linux || Virtualization (VMware,OLVM) || Winserver. Certifie...محافظة بغداد بغداد العراق

Divya sai m

Information Security and Privacy AnalystDüsseldorf, North Rhine-Westphalia, Germany

Sandra le berre

Coordinatrice-Gestionnaire de Tiers-LieuLimoges, Nouvelle-Aquitaine, France

Jhatashia stevenson

Program Management Sr. Analyst at CignaNashville, Tennessee, United States

...

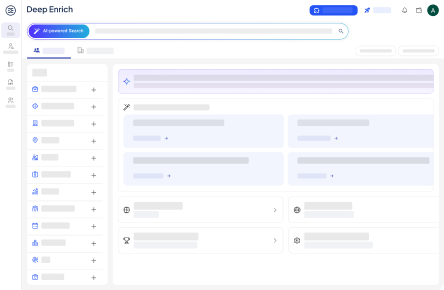

Deep Enrich

Deep Enrich